meoconandung2024

Thành viên

- Tham gia

- 16/6/2024

- Bài viết

- 17

Tại sự kiện Tech Day vừa diễn ra, AMD đã thông tin chi tiết về vi Kiến Trúc của CPU Zen 5, tiếp tục cải thiện IPC so với với thế hệ trước, điều mà công ty đã theo đuổi từ khi kiến trúc Zen ra đời đến nay. Cải thiện dễ thấy nhất chính là giúp các mẫu CPU Zen 5 như Ryzn 9000 và cả Ryzen AI 300 dành cho laptop có hiệu năng lẫn hiệu suất cao hơn so với thế hệ trước.

Điểm nhấn quan trọng nhất trên vi kiến trúc Zen 5 chính là tăng cường tốc độ lấy lệnh nhằm cải thiện khả năng dự đoán nhánh. Với kỹ thuật cải tiến dual-pipe, tốc độ lấy lệnh sẽ được cải tiến đáng kể, giảm độ trễ tính từ lúc lệnh được yêu cầu tới lúc thực thi, đặc biệt là trong các tình huống dự đoán nhánh chính xác, từ đó giúp việc thực thi lệnh nhanh hơn và cải thiện hiệu suất tổng thể của toàn bộ CPU.

Điểm quan trọng tiếp theo trong vi kiến trúc Zen 5 chính là khả năng thực thi số nguyên INT8 được nâng cấp đáng kể so với Zen 4 nhờ vào tính năng 8-wide dispatch/retire system. Hệ thống này có thể gởi và hoàn tất 8 lệnh trong mỗi chu kỳ xung nhịp, giúp tăng đáng kể thông lượng và tận dụng hiệu quả tính song song của các chương trình, thực hiện nhiều lệnh độc lập cùng lúc.

Mặt khác, Zen 5 còn được trang bị 6 ALU và 3 bộ multiplier, tăng cường khả năng xử lý đồng thời nhiều phép tính số học hơn nhằm cải thiện tốc độ tính toán của CPU. Ngoài ra, bộ lập lịch ALU cũng được cải tiến nhằm quản lý và phân phối công việc cho các ALU một cách hiệu quả, đảm bảo các ALU luôn được sử dụng tối đa, tránh tình trạng đứa thì nhiều việc còn đứa thì ngồi không. Bộ đệm Execution Window trên Zen 5 cũng được cải tiến để chứa các lệnh đã được giải mã và sẵn sàng thực thi, giúp CPU xem xét nhiều lệnh hơn cùng lúc nhằm tối ư hóa thứ tự thực thi để tăng hiệu suất tổng thể của CPU Zen 5.

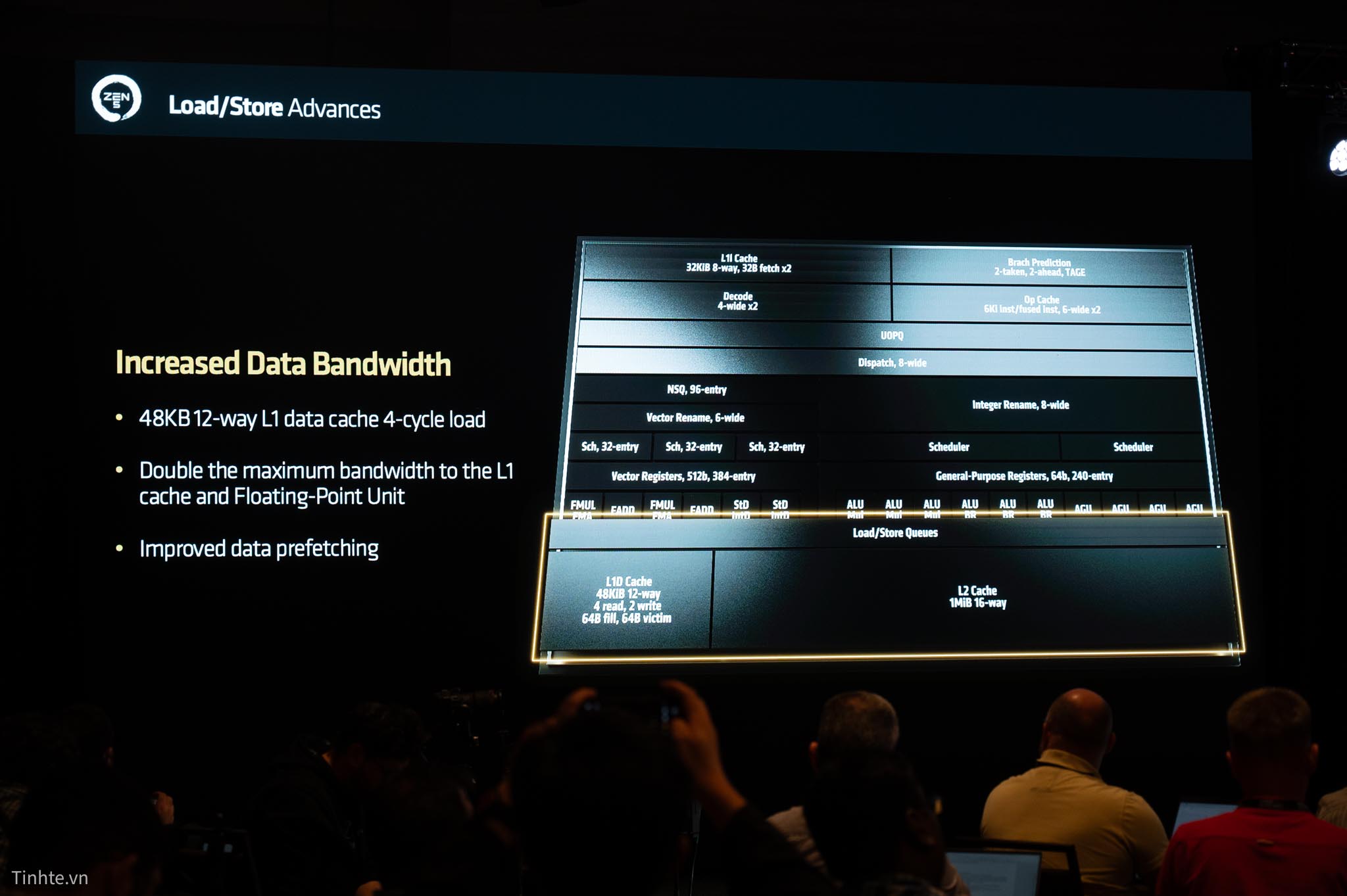

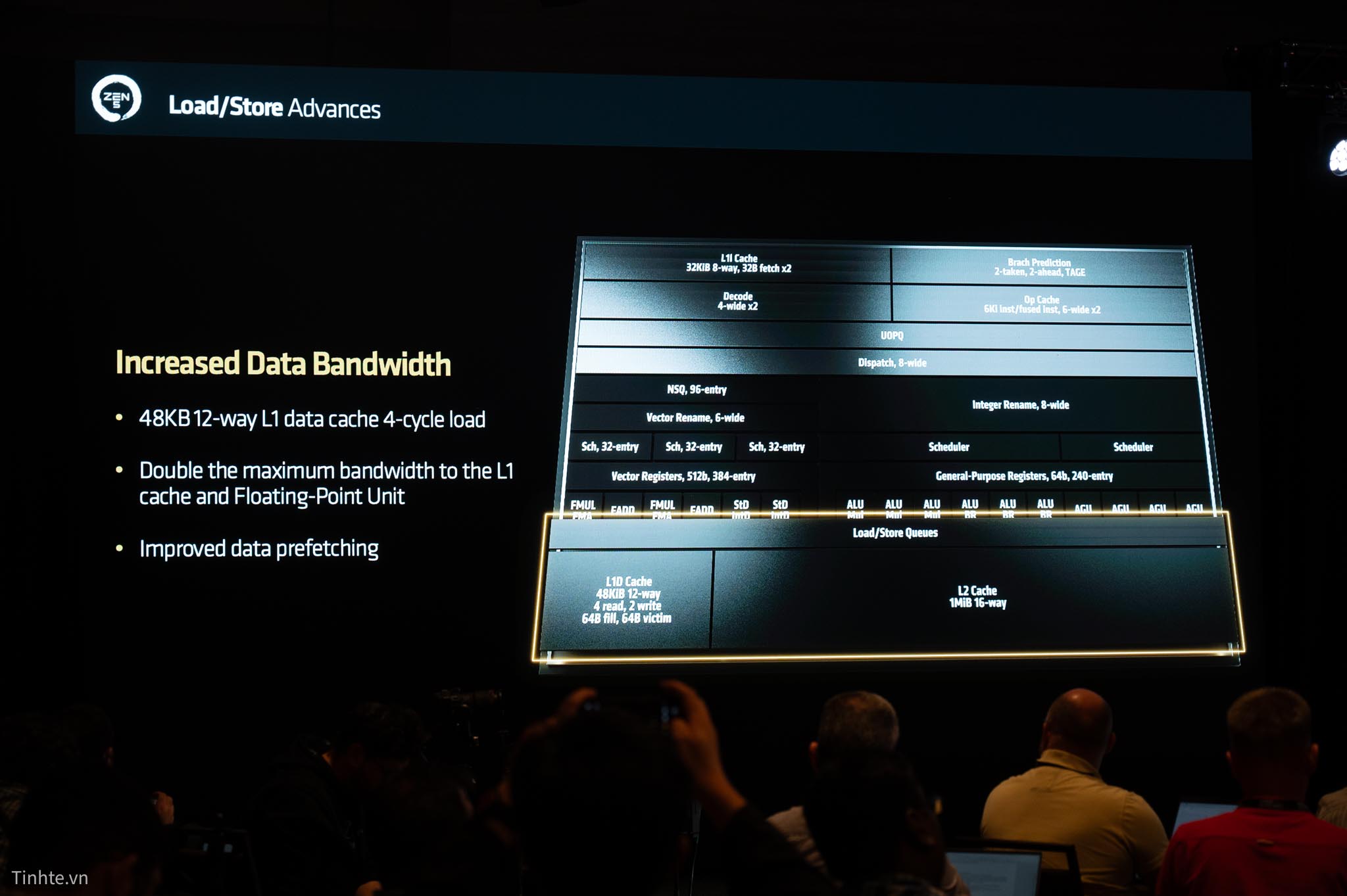

Băng thông dữ liệu của vi kiến trúc Zen 5 cũng được cải thiện hơn so với Zen 4. Zen 5 được trang bị cache L1 12 way dung lượng 48KB với khả năng đáp ứng được 4 chu kỳ. Với gấp đôi băng thông tối đa, Cache L1 đảm bảo tốc độ nhanh hơn gấp đôi so với Zen 4. Ngoài ra FPU (unit xử lý đấu phẩy động) cũng được tấp gấp đôi giúp CPU en 5 thực hiện các phép tính số học nhanh hơn so với thế hệ trước. AMD cho biết trình nạp trước dữ liệu (data fetcher) cũng được cải tiến nhằm tăng cường hiệu suất và độ chính xác dự đoán dữ liệu sẽ được dùng tiếp theo, góp phần tăng tốc độ truy cập dữ liệu, cải thiện độ trễ và nâng cao hiệu suất tổng thể.

Trước đây trên vi kiến trúc Zen 4 mặc dù đã hỗ trợ AVX-512 nhằm thực thi các phép tính số học và logic trên các vector dữ liệu 512 bit, tuy nhiên AMD cho biết Zen 5 sẽ được trang bị datapath đầy đủ hơn, cho phép xử lý các lệnh AVX-512 hiệu quả hơn. Hiện tại, Zen 5 đã có thể tính toán trên các vector 512bit trong 1 chu kỳ duy nhất thay vì chia nhỏ ra như trước đây.

Đồng thời, Zen 5 cũng được trang bị 6 pipeline chuyên biệt để xử lý các lệnh AVX-512 với độ trễ phép cộng số thực FADD chỉ 2 chu kỳ, giúp tăng tốc độ tính toán dấu phẩy động. Kết quả cuối cùng của 2 cải tiến này chính là tăng tốc đáng kể cho các ứng dụng xử lý dữ liệu lớn, đồ họa, AI cũng như các ứng dụng tính toán đòi hỏi hiệu năng cao khác.

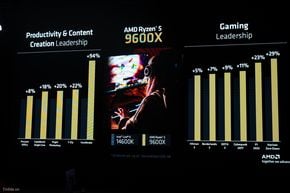

Tổng thể, AMD tuyên bố những cải tiến IPC trên Zen 5 giúp hiệu năng trung bình đạt mức cao hơn 16% so với Zen 4 trước đây. Như trong kết quả trên, AMD cho biết các kết quả thử nghiệm cho thấy hiệu năng xử lý các ứng dụng / game như Farcry 6, Speedometer, LoL,... đều được tăng từ 10% so với kiến trúc trước. Đặc biệt, điểm số Geekbench 5.4 AES-XTS trên Zen 5 tăng 35% - một mức tăng thực sự ấn tượng về hiệu suất.

Quảng cáo

![[IMG] [IMG]](https://photo2.tinhte.vn/data/attachment-files/2024/07/8394602_AMD_Tech_day-211.jpg)

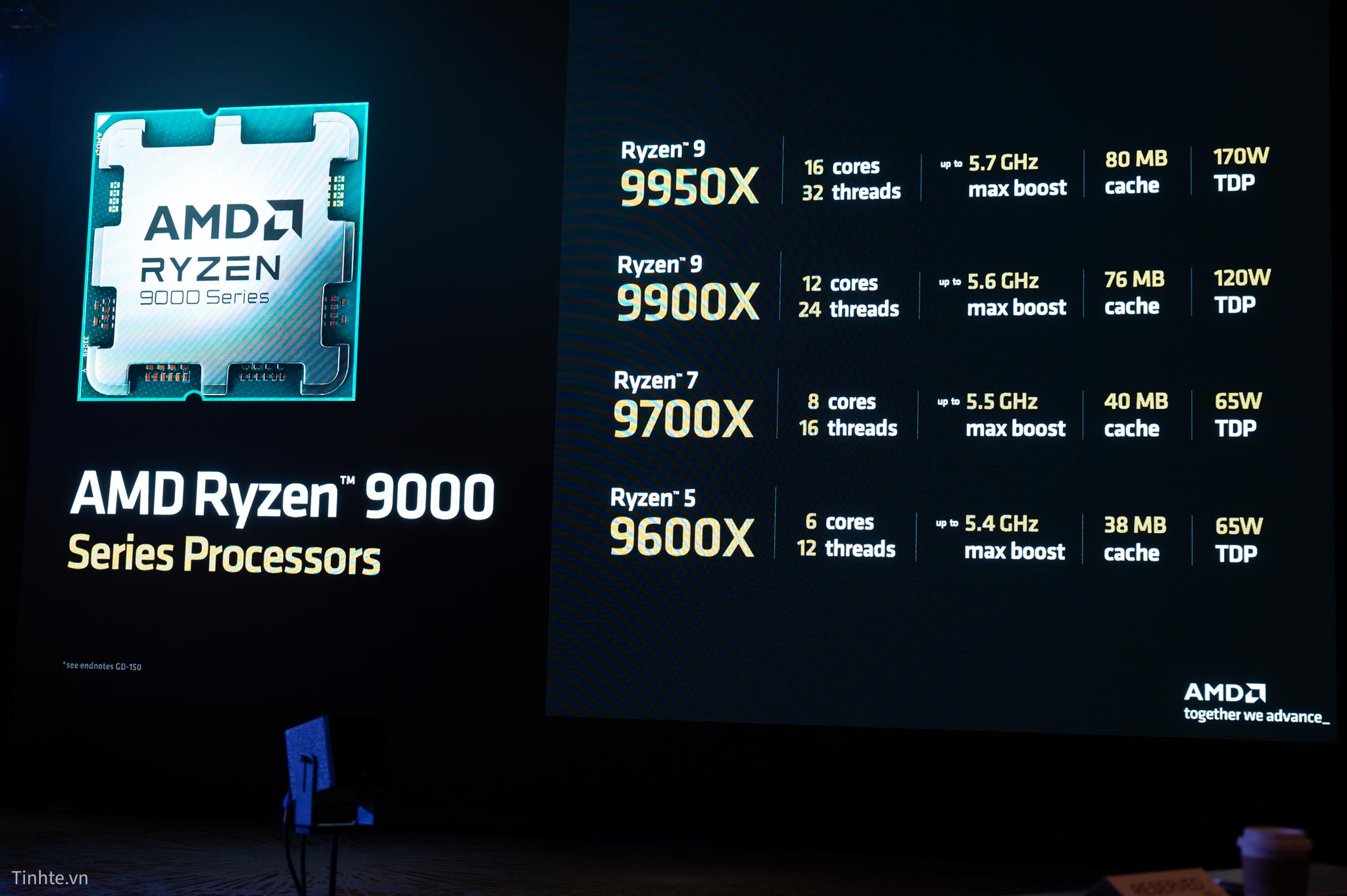

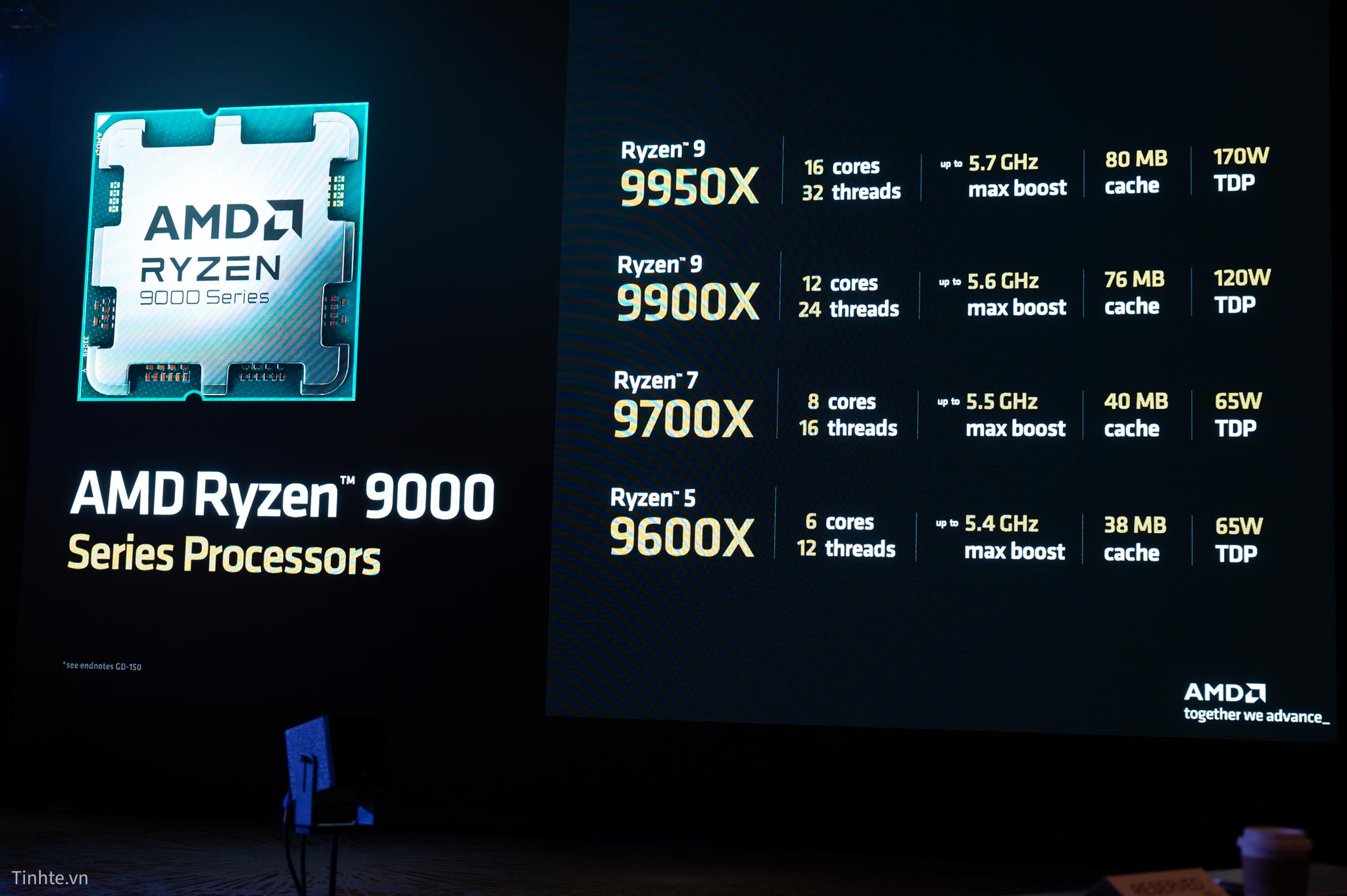

Các mẫu CPU thuộc Series Ryzen 9000 dành cho desktop sử dụng kiến trúc Zen 5 hoàn chỉnh sẽ được sản xuất trên tiến trình TSMC 4nm, dự kiến chính thức ra mắt vào 31/7 sắp tới.

Chi tiết hơn, chúng ta sẽ có 4 phiên bản. Mẫu cao cấp nhất sẽ là Ryzen 9 9950X, 16 nhân, xung nhịp boost đạt 5.7 Ghz, 80MB cache chia cho 64MB L3, 16M cho L2, mỗi nhân L2 1 MB và có mức TDP là 170W. Trong khi đó mẫu Ryzen 9 9900X sẽ có 12 nhân, xung tối đa 5.6GHz, 64MB L3 cache và TDP đạt 120W. Kế tiếp sẽ là mẫu Ryzenn 7 7900X với 8 nhân, xung tối đa 5.5GHz, 32<B L3 cache và TDP đạt mức 65W. Cuối cùng là mẫu entry Ryzen 5 9600X với 6 nhân, xung nhịp tối đa 5.4Ghz, 32 MB L3 cache và TDP đạt mức 65W.

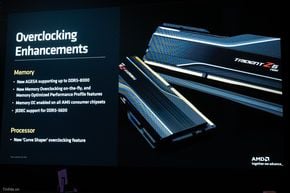

Tất nhiên, tất cả các mẫu CPU Zen 5 lần ày lẫn các mẫu AMD 7000 series đều sẽ sử dụng bo AMD5 với socket LGA1718. Ngoài ra tại sự kiện, AMD cũng giới thiệu một tính năng mới đối với nền tảng Ryzen 9000 và Zen 5 là Curve Shaper cho việc ép xung (tất nhiên là 9000 vẫn sẽ hỗ trợ Curve Optimizer giới thiệu hồi Zen 3 và dòng 5000 đến giờ).

Về cơ bản thì Curve Shaper sẽ là bảng nâng cấp dành riêng cho các CPU Zen 5, cho phép ngươi dùng tinh chỉnh các mức điện áp trên 15 mức xung và nhiệt độ khác nhau, từ đó cho phép kiểm soát điện, Vcore và xung chi tiết hơn trong khi vẫn duy trì được sự ổn định. Tóm lại, tính năng Curve Shaper cho phép người dùng đẩy các con CPU Ryzen 9000 lên giới hạn của nó nhưng vẫn duy trì ổn định và cả tính tiết liệm năng lượng để boot.

Điểm nhấn quan trọng nhất trên vi kiến trúc Zen 5 chính là tăng cường tốc độ lấy lệnh nhằm cải thiện khả năng dự đoán nhánh. Với kỹ thuật cải tiến dual-pipe, tốc độ lấy lệnh sẽ được cải tiến đáng kể, giảm độ trễ tính từ lúc lệnh được yêu cầu tới lúc thực thi, đặc biệt là trong các tình huống dự đoán nhánh chính xác, từ đó giúp việc thực thi lệnh nhanh hơn và cải thiện hiệu suất tổng thể của toàn bộ CPU.

Điểm quan trọng tiếp theo trong vi kiến trúc Zen 5 chính là khả năng thực thi số nguyên INT8 được nâng cấp đáng kể so với Zen 4 nhờ vào tính năng 8-wide dispatch/retire system. Hệ thống này có thể gởi và hoàn tất 8 lệnh trong mỗi chu kỳ xung nhịp, giúp tăng đáng kể thông lượng và tận dụng hiệu quả tính song song của các chương trình, thực hiện nhiều lệnh độc lập cùng lúc.

Mặt khác, Zen 5 còn được trang bị 6 ALU và 3 bộ multiplier, tăng cường khả năng xử lý đồng thời nhiều phép tính số học hơn nhằm cải thiện tốc độ tính toán của CPU. Ngoài ra, bộ lập lịch ALU cũng được cải tiến nhằm quản lý và phân phối công việc cho các ALU một cách hiệu quả, đảm bảo các ALU luôn được sử dụng tối đa, tránh tình trạng đứa thì nhiều việc còn đứa thì ngồi không. Bộ đệm Execution Window trên Zen 5 cũng được cải tiến để chứa các lệnh đã được giải mã và sẵn sàng thực thi, giúp CPU xem xét nhiều lệnh hơn cùng lúc nhằm tối ư hóa thứ tự thực thi để tăng hiệu suất tổng thể của CPU Zen 5.

Băng thông dữ liệu của vi kiến trúc Zen 5 cũng được cải thiện hơn so với Zen 4. Zen 5 được trang bị cache L1 12 way dung lượng 48KB với khả năng đáp ứng được 4 chu kỳ. Với gấp đôi băng thông tối đa, Cache L1 đảm bảo tốc độ nhanh hơn gấp đôi so với Zen 4. Ngoài ra FPU (unit xử lý đấu phẩy động) cũng được tấp gấp đôi giúp CPU en 5 thực hiện các phép tính số học nhanh hơn so với thế hệ trước. AMD cho biết trình nạp trước dữ liệu (data fetcher) cũng được cải tiến nhằm tăng cường hiệu suất và độ chính xác dự đoán dữ liệu sẽ được dùng tiếp theo, góp phần tăng tốc độ truy cập dữ liệu, cải thiện độ trễ và nâng cao hiệu suất tổng thể.

Trước đây trên vi kiến trúc Zen 4 mặc dù đã hỗ trợ AVX-512 nhằm thực thi các phép tính số học và logic trên các vector dữ liệu 512 bit, tuy nhiên AMD cho biết Zen 5 sẽ được trang bị datapath đầy đủ hơn, cho phép xử lý các lệnh AVX-512 hiệu quả hơn. Hiện tại, Zen 5 đã có thể tính toán trên các vector 512bit trong 1 chu kỳ duy nhất thay vì chia nhỏ ra như trước đây.

Đồng thời, Zen 5 cũng được trang bị 6 pipeline chuyên biệt để xử lý các lệnh AVX-512 với độ trễ phép cộng số thực FADD chỉ 2 chu kỳ, giúp tăng tốc độ tính toán dấu phẩy động. Kết quả cuối cùng của 2 cải tiến này chính là tăng tốc đáng kể cho các ứng dụng xử lý dữ liệu lớn, đồ họa, AI cũng như các ứng dụng tính toán đòi hỏi hiệu năng cao khác.

Tổng thể, AMD tuyên bố những cải tiến IPC trên Zen 5 giúp hiệu năng trung bình đạt mức cao hơn 16% so với Zen 4 trước đây. Như trong kết quả trên, AMD cho biết các kết quả thử nghiệm cho thấy hiệu năng xử lý các ứng dụng / game như Farcry 6, Speedometer, LoL,... đều được tăng từ 10% so với kiến trúc trước. Đặc biệt, điểm số Geekbench 5.4 AES-XTS trên Zen 5 tăng 35% - một mức tăng thực sự ấn tượng về hiệu suất.

Quảng cáo

![[IMG] [IMG]](https://photo2.tinhte.vn/data/attachment-files/2024/07/8394602_AMD_Tech_day-211.jpg)

Các mẫu CPU thuộc Series Ryzen 9000 dành cho desktop sử dụng kiến trúc Zen 5 hoàn chỉnh sẽ được sản xuất trên tiến trình TSMC 4nm, dự kiến chính thức ra mắt vào 31/7 sắp tới.

Chi tiết hơn, chúng ta sẽ có 4 phiên bản. Mẫu cao cấp nhất sẽ là Ryzen 9 9950X, 16 nhân, xung nhịp boost đạt 5.7 Ghz, 80MB cache chia cho 64MB L3, 16M cho L2, mỗi nhân L2 1 MB và có mức TDP là 170W. Trong khi đó mẫu Ryzen 9 9900X sẽ có 12 nhân, xung tối đa 5.6GHz, 64MB L3 cache và TDP đạt 120W. Kế tiếp sẽ là mẫu Ryzenn 7 7900X với 8 nhân, xung tối đa 5.5GHz, 32<B L3 cache và TDP đạt mức 65W. Cuối cùng là mẫu entry Ryzen 5 9600X với 6 nhân, xung nhịp tối đa 5.4Ghz, 32 MB L3 cache và TDP đạt mức 65W.

Tất nhiên, tất cả các mẫu CPU Zen 5 lần ày lẫn các mẫu AMD 7000 series đều sẽ sử dụng bo AMD5 với socket LGA1718. Ngoài ra tại sự kiện, AMD cũng giới thiệu một tính năng mới đối với nền tảng Ryzen 9000 và Zen 5 là Curve Shaper cho việc ép xung (tất nhiên là 9000 vẫn sẽ hỗ trợ Curve Optimizer giới thiệu hồi Zen 3 và dòng 5000 đến giờ).

Về cơ bản thì Curve Shaper sẽ là bảng nâng cấp dành riêng cho các CPU Zen 5, cho phép ngươi dùng tinh chỉnh các mức điện áp trên 15 mức xung và nhiệt độ khác nhau, từ đó cho phép kiểm soát điện, Vcore và xung chi tiết hơn trong khi vẫn duy trì được sự ổn định. Tóm lại, tính năng Curve Shaper cho phép người dùng đẩy các con CPU Ryzen 9000 lên giới hạn của nó nhưng vẫn duy trì ổn định và cả tính tiết liệm năng lượng để boot.